Abstract: This paper implements a set-top box source decoder with SC2005 as the main chip, and connects the decoder to the L64768 front end to form a complete set-top box solution conforming to the DVBC standard; it can decode audio and video streams conforming to the MPEG-2 standard. It is also compatible with analog TV reception in PAL/NTSC/SECAM format.

Keywords: DVB-C; set-top box; source decoder; SC2005

introduction

In recent years, the process of digitalization of China's radio and television has been significantly accelerated, which has directly triggered a huge market demand for set-top boxes, highlighting its importance. In the development of set-top boxes, the development of the source decoder is the foundation and core of the entire development work. With the introduction of the card separation policy, the versatility and complexity of the source decoder has made it more important in the development of set-top box terminals. This paper discusses the design and implementation of a digital cable set-top box source decoder conforming to the DVBC standard.

Overall plan

The set top box can be roughly divided into two functional parts: a channel demodulation decoding part and a source decoding part. The channel part, the front end, is responsible for demodulation reception and channel decoding of the digital television signal. Due to the difference in front-end, set-top boxes can be divided into digital satellite set-top boxes, digital terrestrial set-top boxes and digital cable set-top boxes.

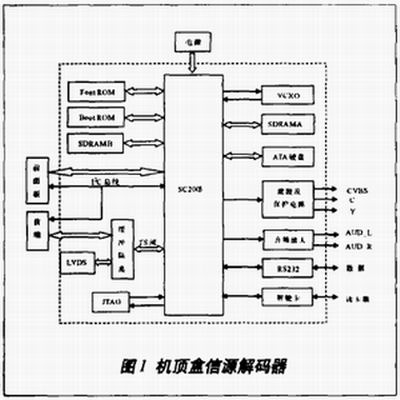

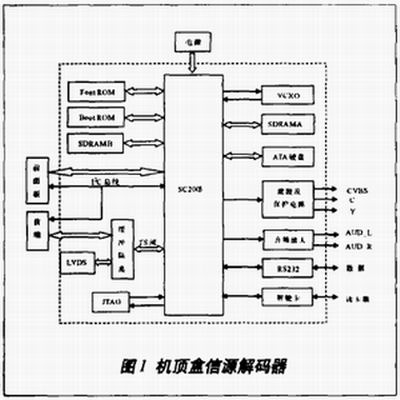

The source decoder is developed for digital cable set-top boxes and will be paired with the L64768 front-end to form a complete set-top box solution compliant with the DVB-C standard. This article uses LSI Logic's SC2005-based second-generation single-chip source decoding solution to achieve decoding. The block diagram of the decoder is shown in Figure 1. It can be divided into four parts according to the function: CPU and storage control subsystem with SC2005 as the core; transport stream demultiplexing and audio and video decoding subsystem; graphics processing and on-screen menu display And output subsystem; peripheral interface subsystem.

Hardware implementation

The startup code of the source decoder is stored in the Flash Boot ROM, and the font used is stored in the Flash Font ROM. The two SDRAM memory interfaces of SC 2 0 0 5 are connected to SDRAMA and SDRAM-B, respectively. After the system is powered up, the boot code saved in the Flash BootROM is transferred to SDRAM-B for execution. The clock is provided by multiplying the 27MHz voltage controlled oscillator. The clock signal generated by the voltage controlled oscillator is shaped by 74LVC14 and sent to the VCXO pin of SC2005, and synchronously restored by the output of the SDET pin. Functions such as transport stream multiplexing, audio and video decoding, and graphics processing are implemented by the corresponding integrated modules in SC2005 in conjunction with external related circuits.

CPU and storage control subsystem

The SC 2 0 0 5 Set Transceiver Demultiplexer L641x8 and the MPEG-2 Audio Video Decoder L64105 integrate the EZ4102 core, 16KB instruction cache and 8KB data cache, which are the core components of the SC2005.

The two 1M × 16 bit Flash ROMs used in this source decoder are AM29LV160DT-70, which are powered by a single power supply. Both read and write and programming use 3.3V and 70ns high read and write time. They are connected to SC2005 via EBUS, address bus A[6:0] is connected to ADDR[7:1] of SC2005, A[19:7] is connected to AD[28:16] of SC2005, data bus DQ[15:0 ] is connected to AD[15:0] of SC2005. There are 35 sectors inside the chip, 4 of which are used as boot sectors, the size is 4k words to 16k words, and the remaining 31 sectors are 32k words; there is a byte/word mode selection BYTE#, which is used in this design. The pin is connected to the high level and the word mode is selected.

The 81MHz/1M × 16bit SDRAMA and the 108MHz/2M × 16bit SDRAMB are connected to the SDRAM memory interface of the CPU through the S-BUS. SDRAM-A is dedicated to storing video frames and related information during MPEG decoding, and SDRAM-B stores information on demultiplexing, OSG and peripheral interface subsystems. Data can be transferred directly between SDRAM-A and SDRAM-B via a DMA engine.

Transport stream demultiplexing and audio and video decoding subsystem

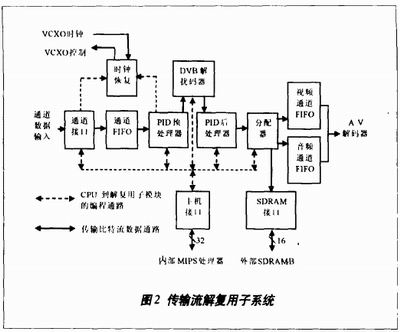

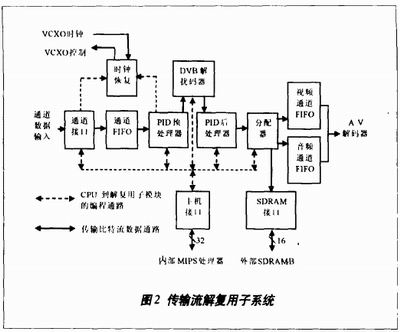

The SC2005 first receives the TS stream from the channel decoder or the code stream generator, and then automatically performs transmission packet synchronization detection. Once the synchronization is established, the transport packet is sent to the PID preprocessor. The PID preprocessor analyzes the incoming transport packets and checks their PID values. Only the PID values ​​that match the PID table can be filtered by the first step, and the unmatched packets are discarded. The transmission packet through the PID filter is sent to the DVB descrambler, and the descrambled packet enters the PID post-processor. After filtering, the audio and video PES data directly enters the A/V decoder, and other data are Sended to the external SDRAM-B circular buffer, the CPU can read data directly from the memory. The block diagram of the transport stream demultiplexing subsystem is shown in Figure 2.

The demultiplexed audio and video PES stream enters the L64105 MPEG-2 decoder through the A/V interface for packet decoding. The L64105 outputs two sets of digital video and digital audio signals. A set of digital video and a set of digital audio signals are output directly. The other set of digital video signals are sent to the video encoder and converted into full TV signal (CVBS) or S terminal signal (Y/C), which is directly sent to the TV after external low-pass filtering; digital audio signal is sent In the audio DAC, it is converted into a stereo analog signal, which is output by external low-pass filtering.

Graphics processing and on-screen menus

Display output subsystem

SC 2 0 0 5 integrates a high-performance OSG (On-Screen Graphics) subsystem that produces text and graphics and overlays them onto decoded video. The OSG subsystem generates a still layer, an OSD layer, and a cursor layer; the decoding subsystem provides a video layer; the mixer/encoder subsystem generates a background color layer, and encodes the above five layers before the video output, thereby displaying the desired The composite video output. This subsystem mixes the graphics and decoded video data from the OSG subsystem and outputs NTSC/PAL/SECAM RGB/YPbPr, CVBS or S-video signals to the TV or monitor.

Peripheral interface subsystem

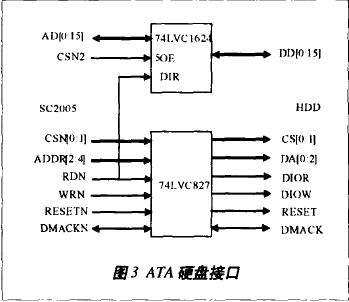

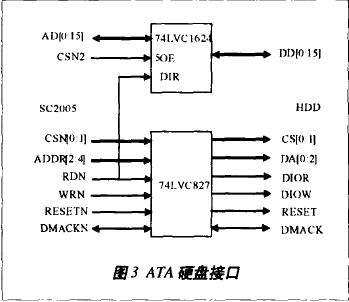

The source decoder integrates an ATA hard disk interface, as shown in Figure 3. Users can use this interface to realize the personal digital video recorder PVR (Personal Video Recorder) function; also can open a large buffer area in the hard disk, while playing digital TV, the program can be stored for several hours in real time. Depending on this caching technology, users can play time-shifted.

The decoder has a TDA8004T smart card interface and an IEEE 1149.1 compliant JTAG module that provides basic debugging capabilities and an LVDS interface for receiving TS streams from the stream generator output. The LVDS signal input by the DB-25 interface is level-shifted by three DS90C032s and enters the decoder. In addition, the system uses a UART for set-top box debugging and software upgrades.

software design

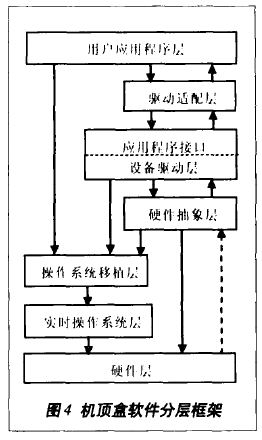

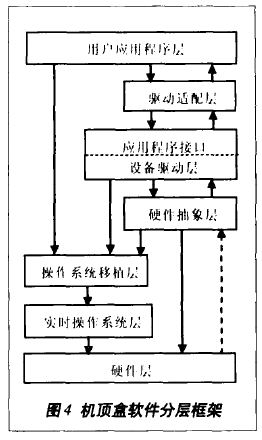

The software system is based on a layered framework, some of which is provided by LSI Logic in its reference software, and other parts need to be developed by the user. The overall structure of the software is shown in Figure 4.

The Real-Time Operating System Layer (RTOS) is the basis for all upper-level program code operations, and is mainly responsible for multi-task scheduling, system resource management, interrupt processing, communication operations, and synchronization processing. This article uses a modular, high-performance real-time operating system, pSOSystem, designed and developed by WindRiver specifically for embedded systems. The RTOS layer uses the board support package (BSP) to interface with the hardware layer.

The Operating System Migration Layer (OSP) implements two main functions: one is to dynamically configure task attributes, such as context switching, priority, etc.; the other is to manage communication between tasks, such as data transfer and synchronization. The hardware abstraction layer (HAL) is responsible for directly programming the hardware registers; the device driver layer (DDL) is a clear and convenient backup and package of the hardware abstraction layer, and provides corresponding drivers for each hardware module, such as the SC2005 exception handling driver. , the driver of the clock service module and the driver of the OSG graphics library. The application interface layer (API) provides API functions for upper-level applications.

The Drive Adaptation Layer (DAL) is a further collection of device driver layer functions that can be applied directly to the application layer through a combination of functions, which acts as an interface. For example, for the operation of Flash, such a driver adaptation layer can be further encapsulated to facilitate the call of the upper application.

The user application layer is the main part of the set-top box user application software and is also the focus of software development. The implementation of all upper-level functions related to the set-top box is completed at this level, such as implementation of user interface functions, implementation of EPG, management of program database, user information input/output control, and software upgrade.

Performance test result

After the source decoder is connected to the L64768 front end, it is tested to achieve the predetermined function. Its performance characteristics are as follows:

The complete system is fully compliant with the DVB-C/MPEG-2 standard

Channel decoding supports 16/32/64/128/2 5 6 QAM with conversion rate: 3 MSPS ~7MSPS

TS Demultiplexer maximum input bit rate: 60Mbps (serial 1) / 7.5Mbps (parallel)

Video decoding resolution: Max720 × 576, support for graphics and subtitles

Audio decoder sampling rate: 32/44.1/48kHz, support 32-level volume adjustment

Support ATA hard disk interface

Conclusion

This paper implements the SC 205-based DVB-C set-top box source decoder, which integrates the personal digital video recorder and is equipped with the L64768 front-end to form a functional prototype that conforms to the standard.

:

Keywords: DVB-C; set-top box; source decoder; SC2005

introduction

In recent years, the process of digitalization of China's radio and television has been significantly accelerated, which has directly triggered a huge market demand for set-top boxes, highlighting its importance. In the development of set-top boxes, the development of the source decoder is the foundation and core of the entire development work. With the introduction of the card separation policy, the versatility and complexity of the source decoder has made it more important in the development of set-top box terminals. This paper discusses the design and implementation of a digital cable set-top box source decoder conforming to the DVBC standard.

Overall plan

The set top box can be roughly divided into two functional parts: a channel demodulation decoding part and a source decoding part. The channel part, the front end, is responsible for demodulation reception and channel decoding of the digital television signal. Due to the difference in front-end, set-top boxes can be divided into digital satellite set-top boxes, digital terrestrial set-top boxes and digital cable set-top boxes.

The source decoder is developed for digital cable set-top boxes and will be paired with the L64768 front-end to form a complete set-top box solution compliant with the DVB-C standard. This article uses LSI Logic's SC2005-based second-generation single-chip source decoding solution to achieve decoding. The block diagram of the decoder is shown in Figure 1. It can be divided into four parts according to the function: CPU and storage control subsystem with SC2005 as the core; transport stream demultiplexing and audio and video decoding subsystem; graphics processing and on-screen menu display And output subsystem; peripheral interface subsystem.

Hardware implementation

The startup code of the source decoder is stored in the Flash Boot ROM, and the font used is stored in the Flash Font ROM. The two SDRAM memory interfaces of SC 2 0 0 5 are connected to SDRAMA and SDRAM-B, respectively. After the system is powered up, the boot code saved in the Flash BootROM is transferred to SDRAM-B for execution. The clock is provided by multiplying the 27MHz voltage controlled oscillator. The clock signal generated by the voltage controlled oscillator is shaped by 74LVC14 and sent to the VCXO pin of SC2005, and synchronously restored by the output of the SDET pin. Functions such as transport stream multiplexing, audio and video decoding, and graphics processing are implemented by the corresponding integrated modules in SC2005 in conjunction with external related circuits.

CPU and storage control subsystem

The SC 2 0 0 5 Set Transceiver Demultiplexer L641x8 and the MPEG-2 Audio Video Decoder L64105 integrate the EZ4102 core, 16KB instruction cache and 8KB data cache, which are the core components of the SC2005.

The two 1M × 16 bit Flash ROMs used in this source decoder are AM29LV160DT-70, which are powered by a single power supply. Both read and write and programming use 3.3V and 70ns high read and write time. They are connected to SC2005 via EBUS, address bus A[6:0] is connected to ADDR[7:1] of SC2005, A[19:7] is connected to AD[28:16] of SC2005, data bus DQ[15:0 ] is connected to AD[15:0] of SC2005. There are 35 sectors inside the chip, 4 of which are used as boot sectors, the size is 4k words to 16k words, and the remaining 31 sectors are 32k words; there is a byte/word mode selection BYTE#, which is used in this design. The pin is connected to the high level and the word mode is selected.

The 81MHz/1M × 16bit SDRAMA and the 108MHz/2M × 16bit SDRAMB are connected to the SDRAM memory interface of the CPU through the S-BUS. SDRAM-A is dedicated to storing video frames and related information during MPEG decoding, and SDRAM-B stores information on demultiplexing, OSG and peripheral interface subsystems. Data can be transferred directly between SDRAM-A and SDRAM-B via a DMA engine.

Transport stream demultiplexing and audio and video decoding subsystem

The SC2005 first receives the TS stream from the channel decoder or the code stream generator, and then automatically performs transmission packet synchronization detection. Once the synchronization is established, the transport packet is sent to the PID preprocessor. The PID preprocessor analyzes the incoming transport packets and checks their PID values. Only the PID values ​​that match the PID table can be filtered by the first step, and the unmatched packets are discarded. The transmission packet through the PID filter is sent to the DVB descrambler, and the descrambled packet enters the PID post-processor. After filtering, the audio and video PES data directly enters the A/V decoder, and other data are Sended to the external SDRAM-B circular buffer, the CPU can read data directly from the memory. The block diagram of the transport stream demultiplexing subsystem is shown in Figure 2.

The demultiplexed audio and video PES stream enters the L64105 MPEG-2 decoder through the A/V interface for packet decoding. The L64105 outputs two sets of digital video and digital audio signals. A set of digital video and a set of digital audio signals are output directly. The other set of digital video signals are sent to the video encoder and converted into full TV signal (CVBS) or S terminal signal (Y/C), which is directly sent to the TV after external low-pass filtering; digital audio signal is sent In the audio DAC, it is converted into a stereo analog signal, which is output by external low-pass filtering.

Graphics processing and on-screen menus

Display output subsystem

SC 2 0 0 5 integrates a high-performance OSG (On-Screen Graphics) subsystem that produces text and graphics and overlays them onto decoded video. The OSG subsystem generates a still layer, an OSD layer, and a cursor layer; the decoding subsystem provides a video layer; the mixer/encoder subsystem generates a background color layer, and encodes the above five layers before the video output, thereby displaying the desired The composite video output. This subsystem mixes the graphics and decoded video data from the OSG subsystem and outputs NTSC/PAL/SECAM RGB/YPbPr, CVBS or S-video signals to the TV or monitor.

Peripheral interface subsystem

The source decoder integrates an ATA hard disk interface, as shown in Figure 3. Users can use this interface to realize the personal digital video recorder PVR (Personal Video Recorder) function; also can open a large buffer area in the hard disk, while playing digital TV, the program can be stored for several hours in real time. Depending on this caching technology, users can play time-shifted.

The decoder has a TDA8004T smart card interface and an IEEE 1149.1 compliant JTAG module that provides basic debugging capabilities and an LVDS interface for receiving TS streams from the stream generator output. The LVDS signal input by the DB-25 interface is level-shifted by three DS90C032s and enters the decoder. In addition, the system uses a UART for set-top box debugging and software upgrades.

software design

The software system is based on a layered framework, some of which is provided by LSI Logic in its reference software, and other parts need to be developed by the user. The overall structure of the software is shown in Figure 4.

The Real-Time Operating System Layer (RTOS) is the basis for all upper-level program code operations, and is mainly responsible for multi-task scheduling, system resource management, interrupt processing, communication operations, and synchronization processing. This article uses a modular, high-performance real-time operating system, pSOSystem, designed and developed by WindRiver specifically for embedded systems. The RTOS layer uses the board support package (BSP) to interface with the hardware layer.

The Operating System Migration Layer (OSP) implements two main functions: one is to dynamically configure task attributes, such as context switching, priority, etc.; the other is to manage communication between tasks, such as data transfer and synchronization. The hardware abstraction layer (HAL) is responsible for directly programming the hardware registers; the device driver layer (DDL) is a clear and convenient backup and package of the hardware abstraction layer, and provides corresponding drivers for each hardware module, such as the SC2005 exception handling driver. , the driver of the clock service module and the driver of the OSG graphics library. The application interface layer (API) provides API functions for upper-level applications.

The Drive Adaptation Layer (DAL) is a further collection of device driver layer functions that can be applied directly to the application layer through a combination of functions, which acts as an interface. For example, for the operation of Flash, such a driver adaptation layer can be further encapsulated to facilitate the call of the upper application.

The user application layer is the main part of the set-top box user application software and is also the focus of software development. The implementation of all upper-level functions related to the set-top box is completed at this level, such as implementation of user interface functions, implementation of EPG, management of program database, user information input/output control, and software upgrade.

Performance test result

After the source decoder is connected to the L64768 front end, it is tested to achieve the predetermined function. Its performance characteristics are as follows:

The complete system is fully compliant with the DVB-C/MPEG-2 standard

Channel decoding supports 16/32/64/128/2 5 6 QAM with conversion rate: 3 MSPS ~7MSPS

TS Demultiplexer maximum input bit rate: 60Mbps (serial 1) / 7.5Mbps (parallel)

Video decoding resolution: Max720 × 576, support for graphics and subtitles

Audio decoder sampling rate: 32/44.1/48kHz, support 32-level volume adjustment

Support ATA hard disk interface

Conclusion

This paper implements the SC 205-based DVB-C set-top box source decoder, which integrates the personal digital video recorder and is equipped with the L64768 front-end to form a functional prototype that conforms to the standard.

:

0 times

Window._bd_share_config = { "common": { "bdSnsKey": {}, "bdText": "", "bdMini": "2", "bdMiniList": false, "bdPic": "", "bdStyle": " 0", "bdSize": "24" }, "share": {}, "image": { "viewList": ["qzone", "tsina", "tqq", "renren", "weixin"], "viewText": "Share to:", "viewSize": "16" }, "selectShare": { "bdContainerClass": null, "bdSelectMiniList": ["qzone", "tsina", "tqq", "renren" , "weixin"] } }; with (document) 0[(getElementsByTagName('head')[0] || body).appendChild(createElement('script')).src = 'http://bdimg.share. Baidu.com/static/api/js/share.js?v=89860593.js?cdnversion=' + ~(-new Date() / 36e5)];

LED Tube Lamp,LED Tube Lighting,LED Tube Lights,LED Emergency Light

LED Bulb Light Bracket Co., Ltd. , http://www.challleds.com