This section explains how to build a basic NIOS II processor system that supports the RT-Thread operating system using Qsys. It also demonstrates how to create an example with two static threads that blink LEDs. The RT-Thread version used is 3.0, and the software environment includes Quartus II 13.0 on a Windows 7 64-bit system. The hardware platform is the Xiaomeige AC620 FPGA development board, with the NIOS II as the embedded processor.

Steps

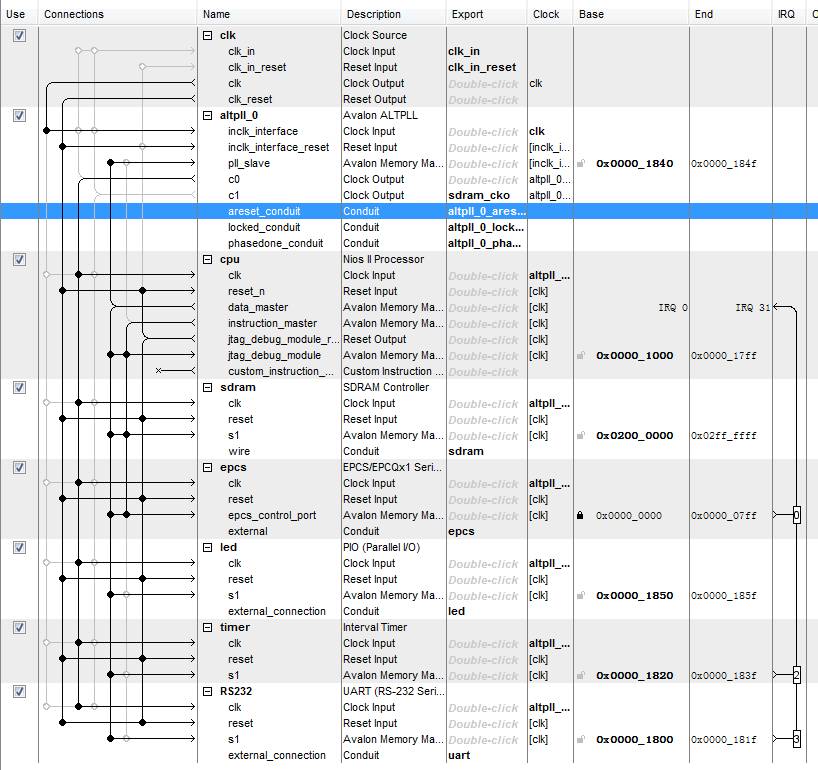

Building a NIOS II CPU system that supports the RT-Thread operating system involves configuring the necessary peripherals in Qsys. Alongside the essential components like the NIOS II processor, RAM (on-chip RAM, SRAM, SDRAM, DDR2), and FLASH memory (EPCS), it's crucial to include UART serial ports, timer peripherals, and a PLL for higher frequency operation. Additionally, a wide-output PIO is added to control the LED lights based on the actual hardware setup.

The system includes the following key peripherals:

- The PLL clock management unit provides two clocks with a 90° phase difference—one for the system logic and one for the SDRAM clock pin (phase -90°).

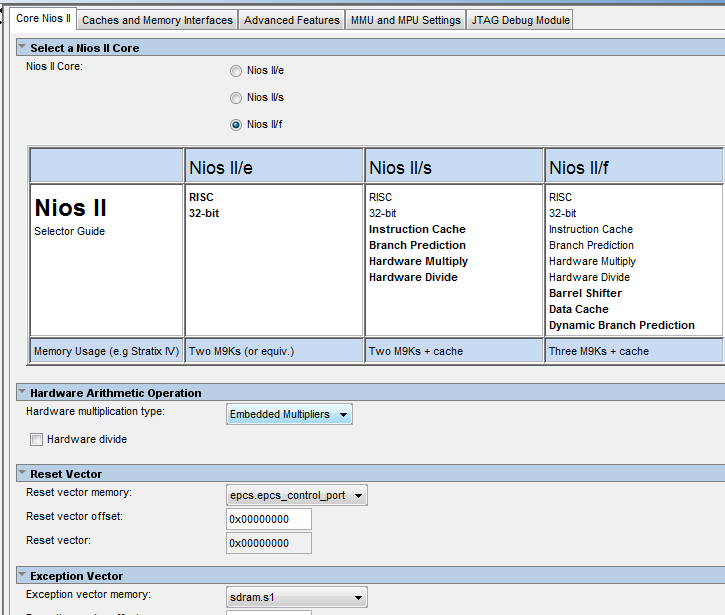

- NIOS II processor, selected as the fast version (f) with default settings.

- SDRAM controller, 16-bit data width, 12-bit row address, 9-bit column address, used for NIOS II instruction and data memory.

- EPCS controller for storing FPGA and NIOS II firmware information.

- UART (RS232) controller for standard input/output, set to 115200 baud rate by default.

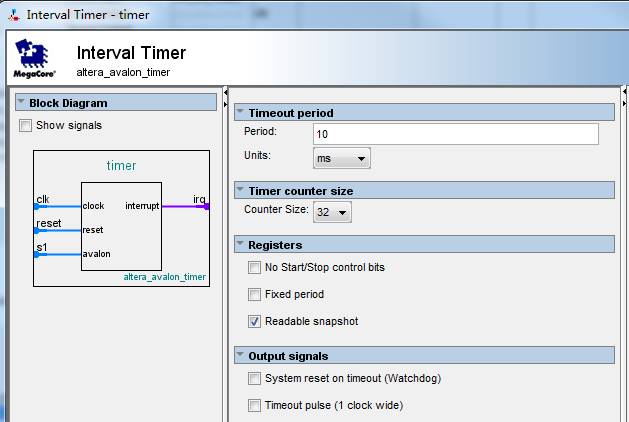

- Timer peripheral, set to 10 milliseconds by default, adjustable via software.

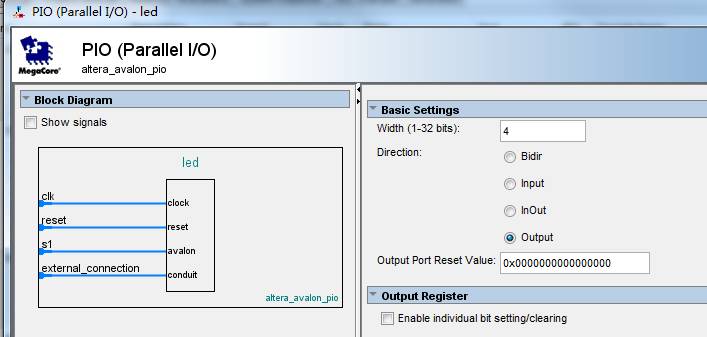

- PIO output port, 4 bits, connected to the four LEDs on the development board.

The figure below shows the minimal NIOS II application system built.

It is important to note that the PIO for the LED is 4 bits and is directly named as "LED." The UART is named "RS232," which corresponds to the relevant code in the RT-Thread BSP file.

NIOS II CPU Configuration

Timer Parameter Settings

UART Controller Settings

LED PIO Settings

Instantiating the CPU System in Quartus II

Designing the Top-Level File

Name the system built in Qsys as "mysystem," generate the HDL file, and add the "mysystem.qsys" file to Quartus II. Create a new Verilog file and update the top-level instantiation information. The improved code is as follows:

module ac620_ghrd (input wire reset_n, input wire clk, output wire [11: 0] sdram_addr, output wire [1: 0] sdram_ba, output wire sdram_cas_n, output wire sdram_cke, output wire sdram_clk, output wire sdram_cs_n, inout wire [15: 0] sdram_dq, output wire [1: 0] sdram_dqm, output wire sdram_ras_n, output wire sdram_we_n, output wire [3: 0] led, input wire uart_rxd, output wire uart_txd, output wire epcs_dclk, output wire epcs_sce, output wire epcs_sdo, input wire epcs_data0); mysystem u0 (.clk_in_reset_reset_n (reset_n), .clk_in_clk (clk), .sdram_addr (sdram_addr), .sdram_ba (sdram_ba), .sdram_cas_n (sdram_cas_n), .sdram_cke (sdram_cke), .sdram_cs_n (sdram_cs_n), .sdram_dq (sdram_dq), .sdram_dqm (sdram_dqm), .sdram_ras_n (sdram_ras_n), .sdram_we_n (sdram_we_n), .led_export (led), .uart_rxd (uart_rxd), .uart_txd (uart_txd), .sdram_cko_clk (sdram_clk), .epcs_dclk (epcs_dclk), .epcs_sce (epcs_sce), .epcs_sdo (epcs_sdo), .epcs_data0 (epcs_data0), .altpll_0_phasedone_conduit_export (), .altpll_0_locked_conduit_export (), .altpll_0_areset_conduit_export () ); endmodule

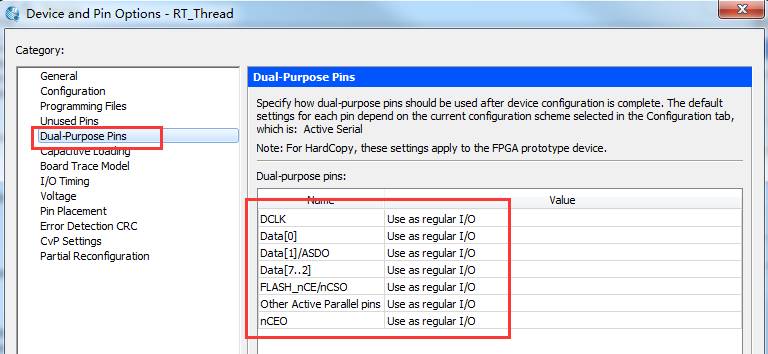

Setting EPCS Pin Functions

Assign pins according to the AC620 FPGA development board’s pinout or silkscreen. Ensure all IO levels are set to 3.3LVTTL to prevent improper SDRAM drive. Also, set the EPCS function to regular IO in Quartus.

Adding an SDC Constraint File

When working on NIOS II-based SOPC development, adding an SDC constraint file is essential to constrain the system clock, ensuring proper layout in Quartus II. Without constraints, the system may fail to operate correctly or experience download issues. The SDC file in this example is simple and can be added to the project.

set_time_format -unit ns -decimal_places 3 create_clock -name {clk} -period 20.000 -waveform {0.000 10.000} [get_ports {clk}] derive_pll_clocks

After adding the constraint, compile the entire project and generate the .sof file.

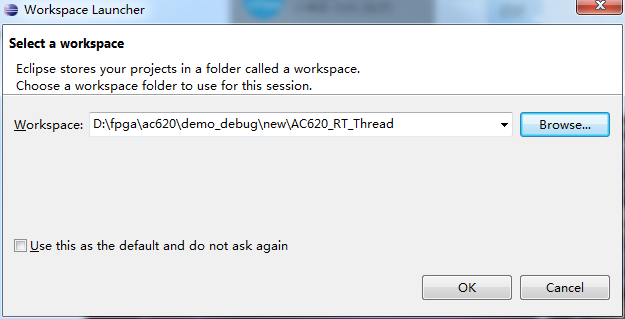

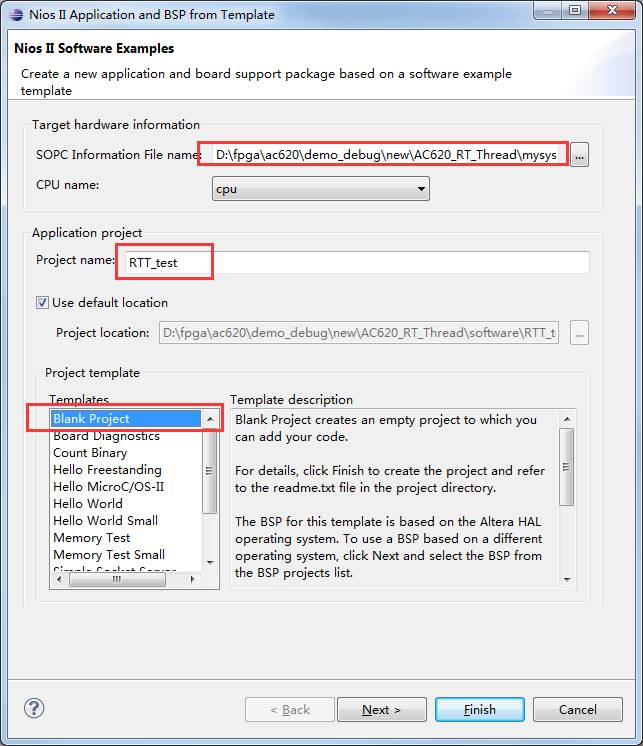

Creating a NIOS II Application Engineering Template

Open the Quartus II-integrated NIOS II software development tool (based on Eclipse) and switch workspaces to the Quartus II project directory.

Create a new blank template project and a BSP project, ensuring the sopcinfo file path is correct.

Porting the RT-Thread Operating System

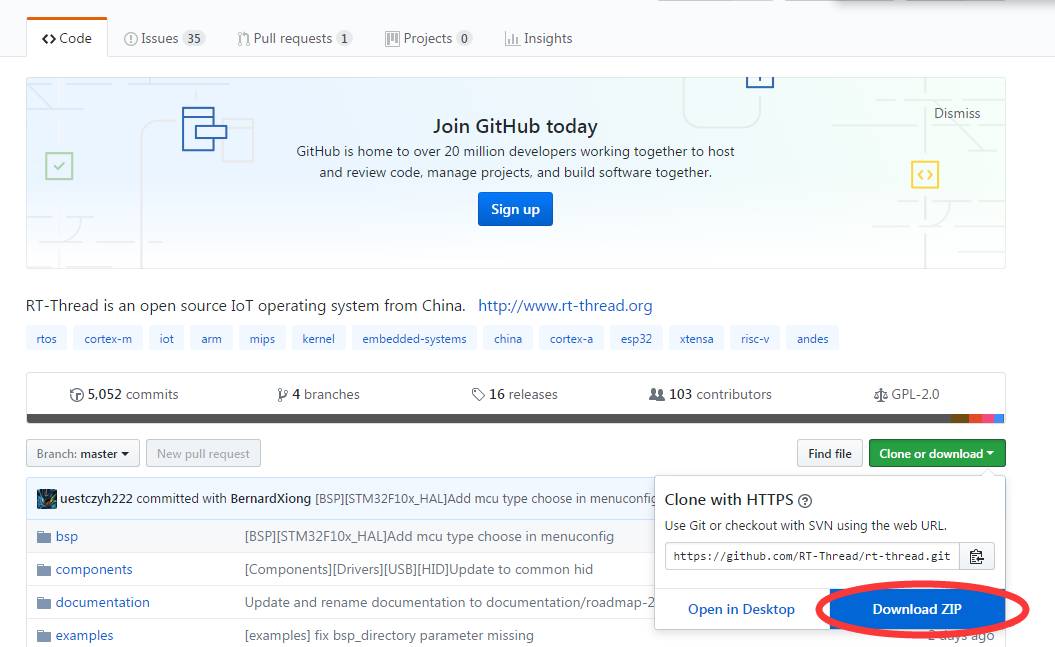

Downloading RT-Thread Source Code

Download the RT-Thread source code from GitHub at https://github.com/RT-Thread/rt-thread, select the master branch, and download the zip file. This file can also be obtained from the provided example zip.

The downloaded file is named “rt-thread-master.zip.â€

Porting the RT-Thread Source Code

Create a new folder called “rt-thread†under the RTT_Test project. Add the src and include folders, and place the nios part of libcpu into the rt-thread folder. Note that libcpu supports various CPUs, but we only need the nios part here. After adding the source code, also include the NIOS II BSP files. These files are located in the bsp/niosii directory. Copy all .c and .h files to the project. The application.c file, containing the main function, should be moved to the root of the software project. The final project structure is shown below (refer to the example project for details).

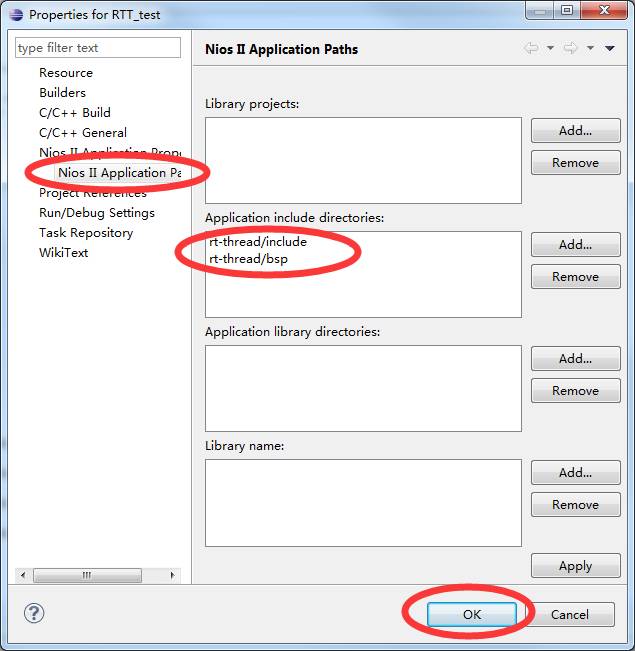

Setting the Header File Search Path

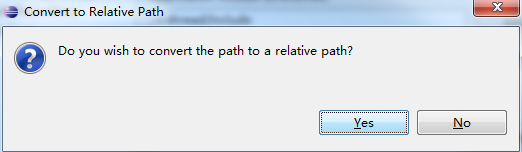

After adding all the files, configure the header search path in the software settings. Right-click the RTT_test project, select Properties, go to Nios II Application Paths, and add the include and bsp folders to the header file path. Confirm and close the dialog. If a relative path prompt appears, select Yes.

At this point, all requirements for running the RT-Thread operating system have been met.

Disabling FINSH Support

Next, open the “rtconfig.h†file in the “rt-thread/bsp†directory. Locate line 80 and add a comment before the “#define RT_USING_FINSH†line to disable the FINSH feature.

Running the RT-Thread Operating System

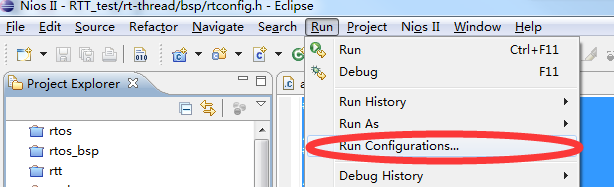

Compiling and Running the Program

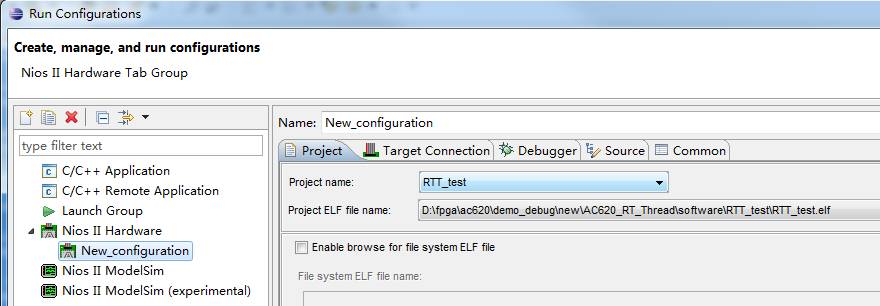

Fully compile the entire project (Ctrl + B). If no errors occur, you will get an ELF file that can be downloaded to the NIOS II CPU. Click “Run > Run Configurations†to open the download window.

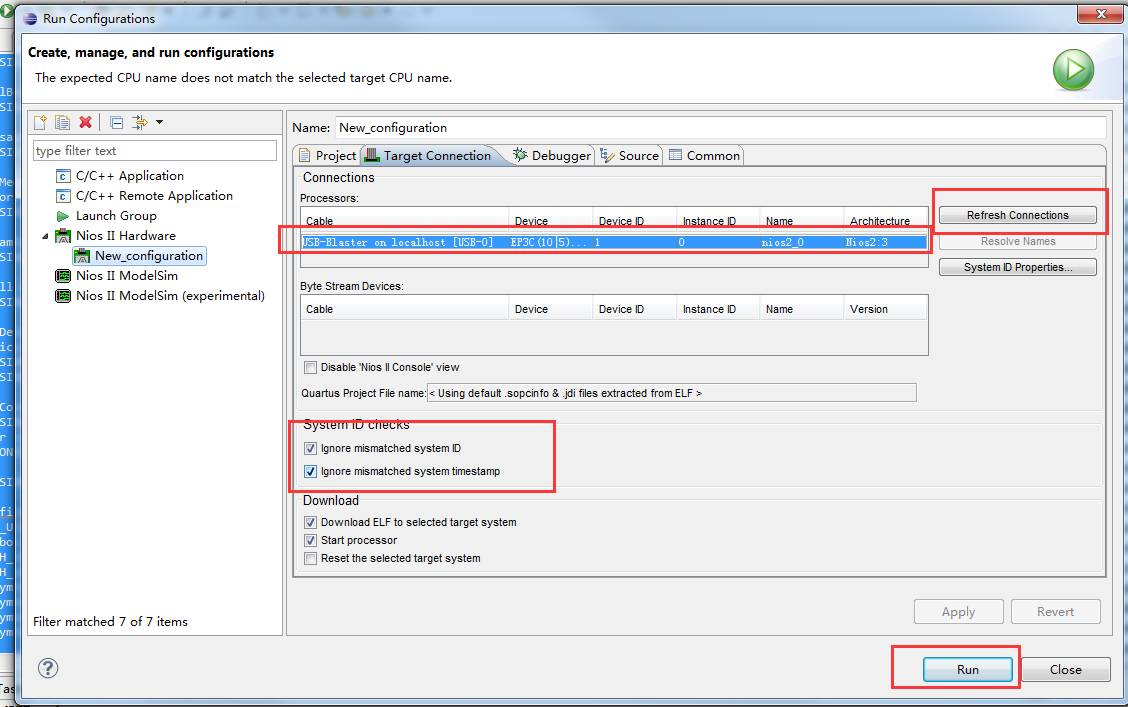

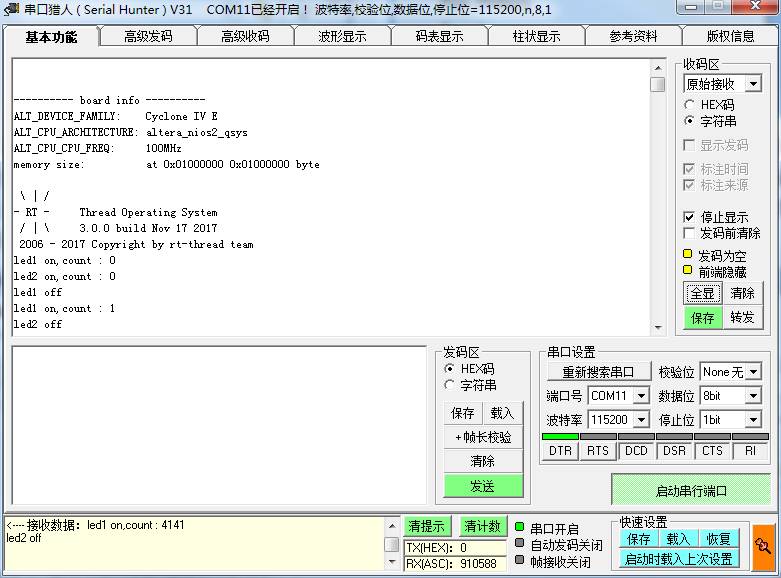

Create a new hardware run configuration, select the RTT_test project, go to the Target Connection tab, and refresh the connection to confirm that the USB Blaster has detected the CPU. Before this, make sure to download the .sof file generated by Quartus II to the development board and connect it to the computer via a Micro USB cable. Open the serial debugging tool, find the corresponding serial port, and set the baud rate to 115200 with ASCII reception.

Check the “Ignore system ID and timestamp†option and click Run to start the software download.

Experimental Results

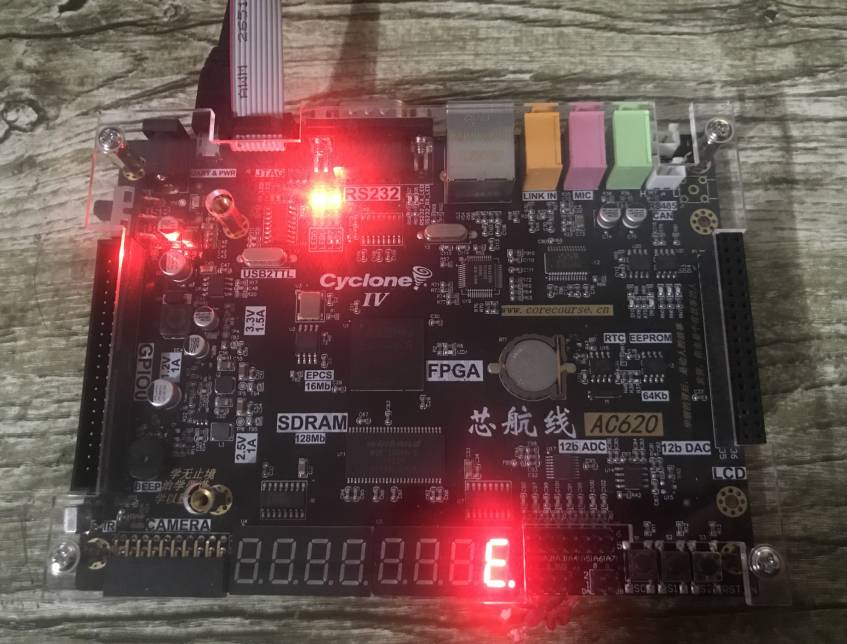

After the download completes, the system output will appear in the serial debugging assistant. At the same time, the four LEDs on the development board will blink cyclically.

220W Medical Adapter,220W Medical Outlet Adapter,220W Medical Ivd Adapter,220W Breast Pump Adapter

Shenzhen Longxc Power Supply Co., Ltd , https://www.longxcpower.com