Some embedded systems use multitasking for operation and control. These systems must provide a mechanism to ensure that running tasks do not disrupt the operation of other tasks. That is to prevent system resources and other tasks from being illegally accessed. Embedded systems have specialized hardware to detect and limit access to system resources. It guarantees ownership of resources. Tasks need to adhere to a set of hardware-maintained rules defined by the operating environment and grant special privileges to monitor and control resource programs at the hardware level. Protected systems proactively prevent one task from using resources from other tasks. Therefore, using hardware proactive monitoring systems provides better protection than coordinating enhanced software processes.

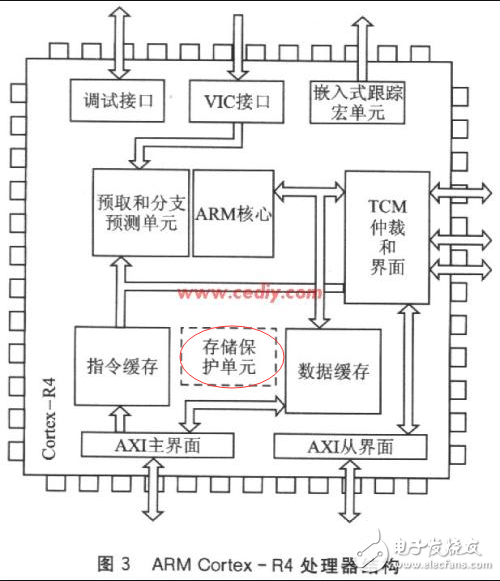

The Memory Protection Unit (MPU) is a type of hardware that is effectively protected by the ARM and provides memory area protection.

MPU function

(1) Protect the memory area.

The MPU in the ARM processor uses "regions" to manage memory cells. A domain is an attribute associated with a storage space that the processor core saves in some registers of the coprocessor CP15. Usually, the number of domains is eight, and the number is from 0 to 7.

The size and start address of the field are stored in register c6 of the CP15. The size can be any power of 2 from 4 KB to 4 GB. The starting address of the domain must be a multiple of its size. For example, a domain defined as 4KB can have a starting address of 0x12345000, and a domain starting address defined as 8KB can only be a multiple of 0x2000.

(2) Overlapping the protected areas.

For an ARM processor, some portion of the storage space can be allocated to more than one area. This means that the domains can overlap. Within overlapping domains, you can set the priority of the domain. Overlapping domains have more flexibility than non-overlapping domains when assigning access rights.

(3) Control access rights.

The operating system can assign more attributes to these domains: access rights, cache, and write cache. The memory can set the access rights of these areas to read/write, read-only, and inaccessible based on the current processor mode (management mode or user mode).

When the processor accesses a domain of the main memory, the MPU compares the access rights attribute of the domain with the current processor mode. If the request conforms to the domain's access criteria, the MPU allows the kernel to read/write the main memory; if the memory request does not have the symbol domain access criteria, an exception signal will be generated.

(4) Output the memory attribute to the system.

The exception signal is sent to the processor core. The processor core executes an exception vector and then jumps to the exception handler. The exception handler determines that the exception type is prefetch or data abort, and then jumps to the corresponding service routine based on the exception type.

How MPU works

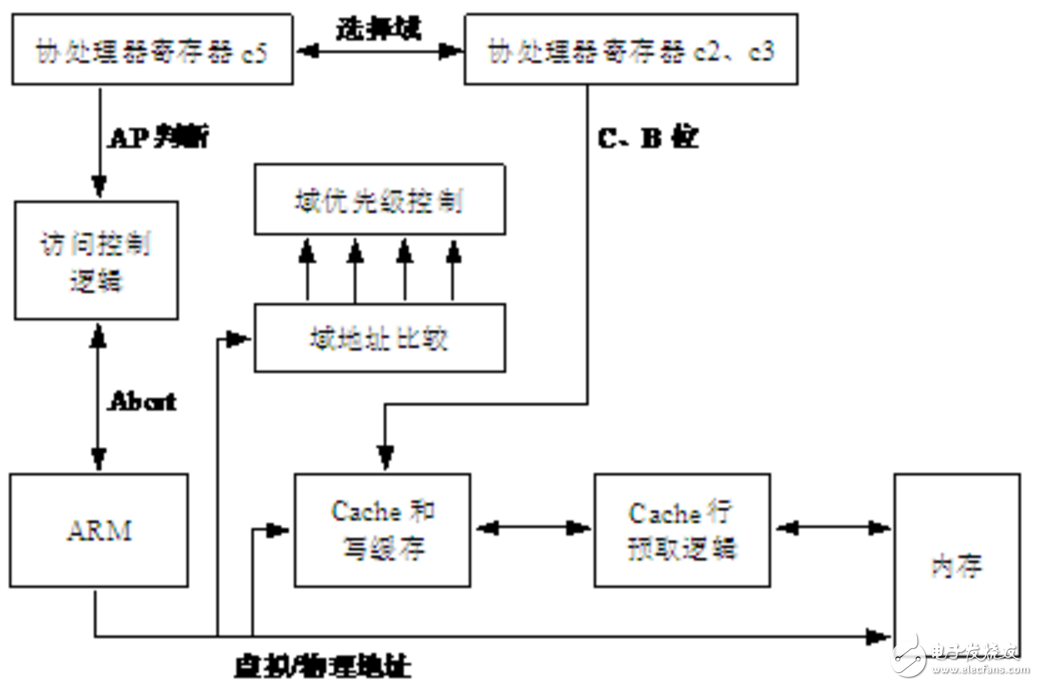

When the ARM processor generates a memory access signal, the memory protection unit MPU will be responsible for checking if the address to be accessed is in the defined domain.

1. If the address is not in any domain, the memory generates an exception. If the kernel prefetch instruction, the MPU generates a prefetch abort exception; if it is a memory data request, a data abort exception is generated.

2. If the address is in multiple domains, the MPU determines the effective level of the domain to determine the access attribute of the storage area. The access attribute can be set in the register of the CP15. The settable bits are C (Cache), B (Buffer), and AP (Access Permission).

The specific definition of these attributes is:

· C and B can control the Cache policy of Cache and write cache attributes. For example, you can set one domain to access memory using a write-back policy, while another domain accesses it in a Cacheless and Writeless Cache mode;

· AP (access permission) determines whether the domain can be accessed. If the domain cannot be accessed in the current processor mode, the MPU will generate a memory access exception.

The KSPOWER brand E series led driver provides various colors like sliver, white, black constant voltage single output LED Drivers with IP20 rating environment protection for indoor use. The led driver junction box accept input 100 to 120V AC voltage, it can make the output wattage of 20W to 96W and accept 12Volt and 24Volt output voltage. The E series flicker free led driver is low profile metal iron housing with 5 years customer service and both ETL/cETL style enclosures. The E series light fixture driver is flicker free design and protections for short circuit, over load, over voltage and over temperature. The E series linear led driver is high PFC function with junction box makes the driver transformer power solutions perfectly easy for installation. The E series led tube light driver is the best choice for LED strips, landscape lighting and led moving sign applications with competitive price.

led driver junction box, flicker free led driver, led dc driver, linear led driver, led tube light driver

Shenzhenshi Zhenhuan Electronic Co., Ltd , https://www.szzhpower.com